# Project 2: Pipelining (10%)

ENEE 646: Digital Computer Design, Fall 2008 Assigned: Thursday, Sep 18; Due: Tuesday, Oct 14

# Purpose

This project is intended to help you understand in detail how a pipelined microprocessor works. You will build a pipelined RiSC-16, complete with *data forwarding*, simple *branch prediction*, and *speculative execution*. The next project will add *caches* and *precise interrupts*. For details on the RiSC-16 pipeline, see the document *The Pipelined RiSC-16* on the class website.

# Pipelines

In the previous project, you built a sequential processor. In that example, the entire instruction is executed before the next clock, at which point the results of the instruction are latched in the register file or data memory. Not surprisingly, this results in a relatively long clock period.

The computer market is not fond of slow clocks, however. Increased clock speeds are possible as the amount of logic between successive latches is decreased. If execution is sliced up into smaller sub-tasks, the clock can run as fast as the longest sub-task. Theoretically, a pipeline of N stages should run with a clock that is N times faster than a sequential implementation. For many reasons, this theoretical limit is never reached, due to latch overhead, sub-tasks of unequal length, etc. Nonetheless, extremely fast clock rates are possible. Slicing up the instruction execution this way is called *pipelining*, and it is exploited to great degree in nearly every aspect of modern computer design, from the processor core to the DRAM subsystem, to the overlapping of transactions on memory and I/O buses, etc.

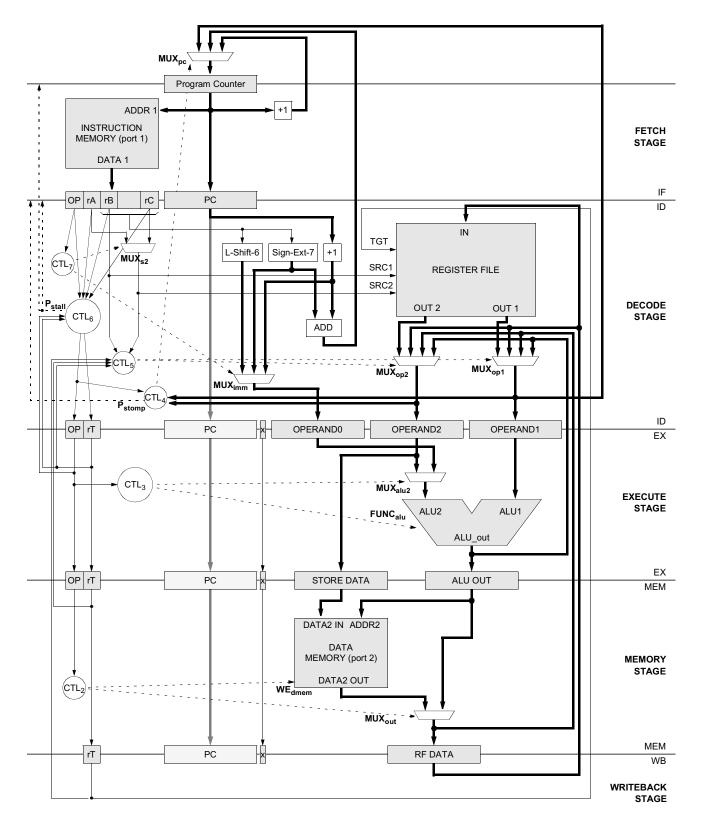

The RiSC-16 pipeline is shown in Fig. 1 on the next page. It is similar to the 5-stage DLX/MIPS pipeline that is described in both *Hennessy & Patterson* and *Patterson & Hennessy*, and it fixes a few minor oversights, such as lack of forwarding to store data, lack of forwarding to comparison logic in decode implementing the 1-instruction delay slot, etc. This pipeline adds in forwarding for store data and eliminates branch delay slots. As in the DLX/MIPS, branches are predicted not taken, though implementations of more sophisticated branch prediction are certainly possible.

In the figure, shaded boxes represent clocked registers; thick lines represent 16-bit buses; thin lines represent smaller data paths; and dotted lines represent control paths. The figure illustrates how pipelining is achieved: the sub-tasks into which instruction execution has been divided are instruction fetch, instruction decode, instruction execute, memory access, and register-file writeback. Each of these sub-tasks, which is executed by dedicated hardware called a pipeline stage, produces intermediate results that must be stored before an instruction may move on to the next stage. By breaking up execution into smaller sub-tasks, it is possible to overlap the different sub-tasks of several different instructions simultaneously. If the intermediate results of the various sub-tasks are not stored, they would be lost: during the next cycle another instruction would use the same hardware for its own task. For instance, after an instruction is fetched, it is necessary to store the fetched instruction somewhere, because the output of the instruction memory will be different on the following cycle—the fetch stage will be fetching a completely different instruction.

The storage locations for the intermediate results are called *pipeline registers*, and the figure illustrates their contents. It is common to label a pipeline register with the two stages that it divides. For example, the pipeline register that divides the instruction fetch (IF) and instruction decode (ID) stages is called the *IF/ID register*; the register that divides the instruction execute (EX) and memory-access (MEM) stages is called the *EX/MEM register*; etc.

Fig. 1: RiSC-16 5-stage pipeline

Note that the DLX/MIPS assumes a half-cycle register-file access, so that the writeback stage completes in the first half of the cycle and the register-file read component of the decode stage happens in the second half of the cycle. This allows data to be forwarded from the writeback stage to the decode stage directly. We do the same thing by making the decode stage longer than any other stage in the pipeline; though it slows down the clock, it reduces the branch penalty from 2 to 1 cycles. Note: whether or not this is a good trade-off can only be determined by simulating both designs against a suite of benchmarks and comparing the results.

### **RiSC-16** Pipeline Registers

| Program Counter<br>IF/ID Register: | The address of the instruction currently being fetched.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INSTR                              | The instruction to execute, with opcode, rA, rB, rC, and immediate fields.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PC                                 | Contains the address of the instruction whose state is contained in this pipeline register. This is used by BEQ and JALR instructions and in handling pipeline interrupts.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ID/EX Register:                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OP                                 | Contains the instruction opcode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| rТ                                 | Contains the instruction's 3-bit target-register identifier, or the 3-bit binary value 000 if the instruction has no target (e.g. SW and BNE instructions).                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PC                                 | Contains the address of the instruction whose state is contained in this pipeline register. This is used by BNE and JALR instructions and in handling pipeline interrupts.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| x                                  | Indicates that the instruction is a HALT instruction (for our purposes, a JALR instruction with any non-zero immediate field).                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| OPERAND0                           | Contains the instruction's immediate operand. If the instruction uses a shifted or sign-extended immediate value (ADDI, LUI, LW, SW, BNE), that value is available immediately and is stored here. In addition, the JALR instruction uses the value PC+1 to store into the register file; because the program counter contains the value PC+1 (relative to IDEX.pc), it can be used for this purpose. Only in instances of JALR execution and branch correction will PC not equal IDEX.pc+1, and in both those cases the contents of the ID/EX register are invalid (the result of a STOMP event). |

| OPERANDI                           | Contains the instruction's first register operand; this is the contents of the register register-file[rB] or a result that has been forwarded from another stage.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| OPERAND2                           | Contains the instruction's second register operand. For ADD and NAND instructions, it is the contents of <i>register-file[rC]</i> . For BNE and SW instructions, it is the contents of <i>register-file[rA]</i> . When appropriate, it contains a result that has been forwarded from another stage                                                                                                                                                                                                                                                                                                |

| EX/MEM Register:                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OP                                 | Contains the instruction opcode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| rT                                 | Contains the instruction's 3-bit target-register identifier, or the 3-bit binary value 000 if the instruction has no target (e.g. SW and BNE instructions).                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PC                                 | If no exceptional instruction is in the pipeline, contains the address of the instruction whose state is contained in this pipeline register. This is used to handle pipeline interrupts.                                                                                                                                                                                                                                                                                                                                                                                                          |

| x                                  | Indicates that the instruction is a HALT instruction (for our purposes, a JALR instruction with any non-zero immediate field).                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| STORE DATA                         | Contains the data to store to DATA MEMORY. Note that if the instruction is not a SW, this information is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ALU OUT                            | Contains the most recent output of the ALU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MEM/WB Register:                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| rТ                                 | Contains the instruction's 3-bit target-register identifier, or the 3-bit binary value 000 if the instruction has no target (e.g. SW and BNE instructions).                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PC                                 | If no exceptional instruction is in the pipeline, contains the address of the instruction whose state is contained in this pipeline register. This is used to handle pipeline interrupts.                                                                                                                                                                                                                                                                                                                                                                                                          |

| x                                  | Indicates that the instruction is a HALT instruction (for our purposes, a JALR instruction with any non-zero immediate field).                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RF DATA                            | Contains the data that will be written to the register file on the following cycle (provided the <b>FT</b> register has a non-<br>zero value).                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### **Control Modules**

These are the descriptions of the various CONTROL modules.

- CTL<sub>I</sub> [removed]

- **CTL2** This module controls both the write-enable line of the data memory and the operation of MUX<sub>out</sub>, which feeds the RF WRITE DATA register and therefore determines what will be written to the register file on the following cycle. Thus, the only input to the control module is the opcode of the instruction. The write-enable line of the data memory is only set if the opcode is SW; otherwise, writing is disabled. MUX<sub>out</sub> only chooses the output of the data memory if the opcode is LW; otherwise, the mux chooses the value of the ALU OUTPUT register in EX/MEM.

- **CTL**<sub>3</sub> This module controls the operation of the ALU and the operation of MUX<sub>alu2</sub>, which serves the ALU's SRC2 input. The module's input is the instruction opcode. The translation from opcode to FUNC<sub>alu</sub> control bus value is dependent on the ALU design. MUX<sub>alu2</sub> chooses between operand2 and immediate value; for all instructions that use immediate values (ADDI, LUI, SW, BNE, JALR), the value in OPERAND0 is chosen. For all other instructions (ADD, NAND), the mux chooses OPERAND2. Note that BNE has been handled by the EX stage, so the value of the mux for a BNE is a dont-care value.

- **CTL**<sup>4</sup> This module controls the STOMP logic and the operation of MUX<sub>pc</sub>. It handles branch mispredictions and JALR instruction execution. The module's inputs are the instruction opcode (after pre-processing by the STALL logic in CTL<sub>6</sub> to ensure that no STALL conditions are in effect) and the two register operands to be fed into the ALU on the next cycle. Having access to these data operands allows the module to determine if the two values are equal or not (i.e. determine if it is appropriate to correct a mispredicted branch instruction). The value of MUX<sub>pc</sub> is set as follows: if the instruction is a BNE and the operands are not equal (or if it is determined that the branch was mis-speculated, if more sophisticated branch prediction is implemented), MUXpc chooses the value of the PC+1+OPERAND0 adder in the decode stage. When this happens, the contents of the IF/ID register are overwritten with a NOP instruction (this is a STOMP event). If the instruction in IF/ID is a JALR, MUX<sub>pc</sub> chooses the output of MUX<sub>op1</sub> and also enables a STOMP event. For all other instructions and instances, MUX<sub>pc</sub> chooses the output of the PC+1 register in IF/ID, and no STOMP event occurs.

- **CTLs** This module handles data forwarding; it controls the operation of MUX<sub>op1</sub> and MUX<sub>op2</sub>, the two muxes responsible for forwarding data from pipeline registers further down the pipe. The control module's input includes the register identifiers from the instruction currently in the decode stage: fields rB and either rA or rC (the rA/rC value is take from the output of MUX<sub>32</sub>, which represents the appropriate register specifier). The rest of the module's inputs are the rT identifiers of the previous three instructions. The control module compares each of the current instruction's input register operands against the output of the previous three instructions. If it is determined that any of the previous three instructions write to any of the registers that the current instruction uses as operands, and if the register specifier in question is non-zero, the data is forwarded from the appropriate pipeline register, giving priority to instructions in higher stages (instructions nearer in time to the current instruction). Note that, if the opcode field of the instruction in the decode stage is not considered, this control module will always forward data based on two register operands; this means that, in the case of the LUI instruction, one of those operands will be invalid. However; because that operand will never be used, forwarding data will not produce incorrect behavior. An optimization could be to consider the opcode to eliminate the activation of unnecessary forwarding paths such as this.

- **CTL**. This module handles the load-use and branch-dependency interlocks and STALL logic (i.e. it sets the opcode OP and register target rT in ID/EX). Its inputs are the opcode and register operand specifiers of the instruction currently in the decode stage (held in the IF/ ID register) and the opcode and target register rT of the instruction in the execute stage. If the instruction currently in the execute stage (held in the ID/EX register) is a LW and targets any register that the instruction in decode uses as a source register, a STALL event is created. The control module's outputs are the OP and rT fields of the ID/EX register, and the Pstall signal, which directs the PC and IF/ID pipeline registers to not latch new values on the next cycle but to retain their values instead. On a pipeline stall, the instructions in the fetch and decode stages are held up, and the register. This amounts to putting an ADD opcode with target register r0 into the OP and rT fields of ID/EX. The module produces a value for the rT register in ID/EX as follows: if the instruction in IF/ID is a type that targets the register file (ADD, ADDI, NAND, LUI, LW, JALR), the value of rA is passed on to the rT register. For SW and BNE instructions, the binary value 000 is passed, indicating that the instruction does not store a value in the register file (this works because r0 is a read-only target).

- CTL<sub>7</sub> This module controls the operation of MUX<sub>imm</sub>, the mux responsible for the contents of the OPERAND0 field of the ID/EX register, and MUX<sub>s2</sub>, the mux responsible for choosing between the rA and rC instruction fields for specifying the second register operand. The control module's input is the opcode of the instruction currently in the decode stage. MUX<sub>imm</sub> chooses between the sign-extended immediate value (to be used for ADDI, LW, SW, and BNE instructions), the left-shifted immediate value (to be used for LUI instructions), and the value PC+1 (to be used for JALR instructions); note that, instead of using a dedicated adder to generate the value of PC+1, the equivalent value can be taken directly from the main program counter (proof of correctness is left to the reader). MUX<sub>s2</sub> chooses rC for ADD and NAND instructions; it chooses rA for all others. The control module simplifies the logic for CTL<sub>5</sub> by eliminating the need for CTL<sub>5</sub> to look at both rA and rC and choose, based on OP.

### **Control Signals**

These signals are exported by the various CONTROL modules and change the direction and flow of data in the pipeline:

FUNCalu This signal instructs the ALU to perform a given function.

- **MUX**<sub>op1</sub> This 2-bit signal controls the mux connected to the OPERANDI component of the ID/EX register, which ultimately feeds into the ALU. The mux chooses between the SRCI output of the register file and the outputs of the previous three instructions, coming from the ALU, the mux at the end of the memory stage, and the RF WRITE DATA component of the MEM/WB register (a value destined for the register file).

- MUX<sub>op2</sub> This 2-bit signal controls the mux connected to the OPERAND2 component of the ID/EX register, which ultimately feeds into the ALU (unless overridden by an immediate value). The mux chooses between the SRC2 output of the register file and the outputs of the previous three instructions, coming from the ALU, the mux at the end of the memory stage, and the RF WRITE DATA component of the MEM/WB register (a value destined for the register file).

- MUX<sub>alu2</sub> This I-bit signal controls the mux connected to the SRC2 ALU input. The mux chooses between a register output and "operand0," which is either an immediate value derived from the instruction word or the value PC+1. The value of "operand0" is chosen for ADDI, LUI, LW, SW, and JALR instructions, and the register operand is chosen for all others (ADD, NAND, BNE).

- MUX<sub>imm</sub> This 2-bit signal controls the mux connected to the OPERAND0 component of the ID/EX register. The mux chooses between the sign-extended immediate value (to be used for ADDI, LW, SW, and JALR instructions), the left-shifted immediate value (to be used for LUI instructions), and the value PC+1 (for JALR instructions).

- MUXout This I-bit signal controls the mux connected to the RF WRITE DATA component of the MEM/WB register, which holds the data to be written to the register file on the following cycle (provided the write-enable bit of the register file is set). The mux chooses between the output of the ALU and the output of the data memory (for LW instructions).

- **MUX**<sub>pc</sub> This 2-bit signal controls the mux connected the PC. The mux chooses between the output of the decode stage's MUX<sub>op1</sub> multiplexor (to be used for JALR instructions), the PC+1+OPERAND0 adder in the decode stage (for instances of BNE instructions that are taken, or branch mispredicts if speculative execution is implemented), and the output of the dedicated adder that produces the sum PC+1 every cycle.

- MUX<sub>s2</sub> This I-bit signal controls the mux connected to the register file's SRC2 operand specifier, a 3-bit signal that determines which of the registers will be read out onto the I6-bit SRC2 data output port. The mux chooses between the rA and rC fields of the instruction word: rC is chosen for ADD and NAND instructions.

- Pstall The *pipeline stall* signal. This I-bit signal indicates that the PC and IF/ID pipeline registers should not latch new data on the next clock edge but instead retain their current contents. The signal causes a pipeline stall event, during which the instructions in the execute and later stages are allowed to move forward one stage, but the topmost two instructions (in fetch and decode stages) are held back, and a NOP instruction is inserted into the ID/EX register.

- **P**stomp The *pipeline stomp* signal. This I-bit signal indicates that the IF/ID pipeline register should not latch the fetched instruction on the next clock but should instead latch a NOP instruction. This is used to implement a branch-taken event (or branch-mispredict event, if speculative execution is implemented), in which a branch instruction (either BNE or JALR) in the decode stage changes the direction of control flow.

- **WE**dmem This I-bit signal enables or disables the write port of the data memory. If the signal is high, the data memory can write a result. If it is low, writing is blocked. It is high for SW instructions.

### Verilog Implementation

On the course website is a skeleton Verilog file that includes definitions for all data structures that you will need, both registers and busses. You will not need to define any new registers, but feel free to define as many new wires as you see fit (e.g., to more finely break down logic blocks). The skeleton file contains definitions for all of the grey blocks shown in Figure 1 (pipeline registers, register file, memory, and ALU), and it contains instantiations of many of the control lines (like P<sub>stall</sub> and P<sub>stomp</sub>) and multiplexer outputs—however, for most it does not give their combinational-logic definitions. The names are roughly equivalent to each other, which should simplify translating from one to the other.

All of the registers are built as modules, each with a clock input, data input and output, reset signal, and a write-enable control signal. Your Verilog code will not need any register assignments; i.e., you need not put any code whatsoever into the "always @(posedge clk)" block at the end of the program, which is simply there to halt processing and print out debugging information.

Your job is to connect everything together—for example, on the positive edge of the clock, the program counter PC should latch a new value, unless the  $P_{stall}$  signal is high. The value to latch comes from the output of the MUX<sub>pc</sub> multiplexer. The data-input bus for the PC is called PC\_\_in. The control signal that conditionally latches a new value is PC\_we. Therefore, in the PC-update stage of your code you would have the following logic:

assign PC\_we = ~Pstall; assign PC\_in = MUXpc\_out;